2018年到来的之初,书僮想跟大家聊聊现今MOS电路应用于显示科技上面的一些知识,去年三月曾经跟大家谈过三大TFT技术的爱恨情仇,这个算是相关知识的延伸。在正式进到应用于TFT上面,不免俗的要先从MOS的基础知识先说起。

来源:Modem Semiconductor Devices of IC

所谓的MOS就是金属-氧化物-半导体所构成的器件,是集成电路当中用途相当广泛的半导体器件,是数字电路、模拟电路和内存等最基本的建构器件。

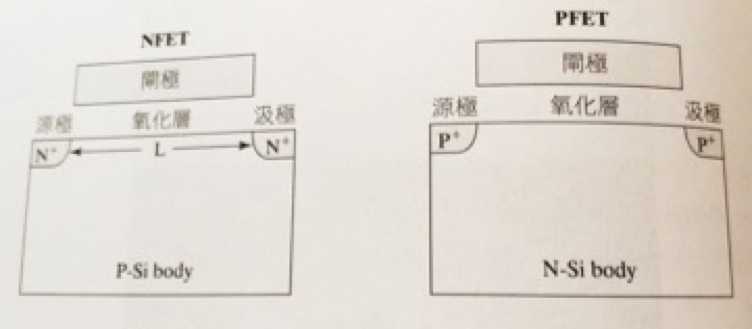

上图左为MOSFET的基本结构,以P型基板然后Source及Drain为N型半导体,担任提供电子或是电洞给予晶体管,或是从晶体管获得载子的任务,同时以金属Gate透过閘極氧化层以电场使用晶体管或MOS结构中反转层导通或关闭的行为,而閘極氧化层做為介電層,將金属Gate與下方的半導體分別形成上下兩電極而構成的電容器。

在右图中也可以看到MOSFET的IV特性,当Gate电压为0时,有着极小的Ioff漏电流,此时为关闭状态;当Gate电压为1.8时,有着极大的Ion的导通电流,此时为开启状态,因此也可以极简的看待MOSFET亦为一种开关,这也是为何又称位场效晶体管(Field effect Transistor)的原因。如下图的示意图。有没有觉得就跟我们常常看到的TFT开关电路一样,那是因为TFT(薄膜晶体管)也是场效应晶体管的种类之一,制作方式亦是在基板上沉积各种不同的薄膜,如半导体主动层、介电质和金属电极层。

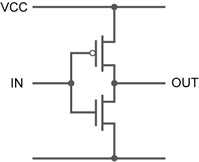

若先从Si材料谈起,a-Si具有较小的电子迁移率,仅用于NMOS。 LTPS具有较大的迁移率,因此可应用于使用「互补p型和n型晶体管」进行电路设计的CMOS架构。看到「互补p型和n型晶体管」进行电路设计的CMOS的这一段长文字了吗?是的,跟文字一样,他是NMOS+PMOS的一种结构,看看下图吧。

来源:Modem Semiconductor Devices of IC

来源:Modem Semiconductor Devices of IC

而a-Si具有较小的电子迁移率,仅用于NMOS。 LTPS具有较大的迁移率,因此可应用于使用互补p型和n型晶体管进行电路设计的CMOS,这又是怎么一回事呢?

提示一:较大的迁移率的优势。

提示二:

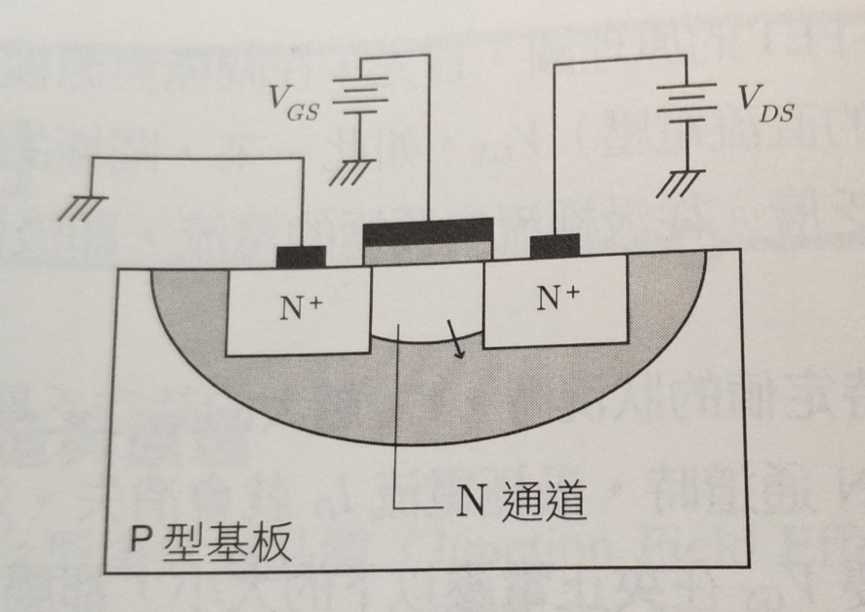

来源:夏普

参考下图来说明,在P型基板上掺杂N型半导体形成Source与Drain,这边写成N+。Gate则在电极与P型基板之间包夹氧化层。当Gate未加电压时极为Vg为零,Source与Drain之间没有通道,就是NPN状态(NP及)PN,两组二极管),若这时在Drain加正电压而Source加负电压,但因为Gate未加电压时极为Vg为零,Source与Drain之间没有通道的建立,因此就算Source与Drain两者之间有电位差,但也不会产生电流。所以可得到一个小结论,在MOS的结构中,Gate下方为一氧化层视为绝缘体,因此几乎不会产生电流。

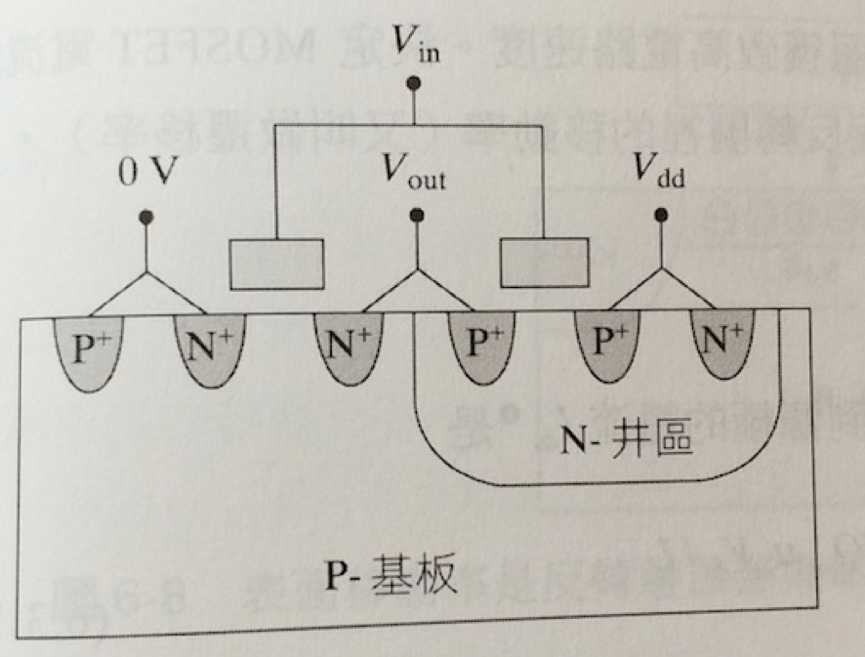

來源:圖解半導體

因此当有PMOS及NMOS在同一个基板上时,若NMOS单一导通但PMOS不通(或PMOS单一导通但NMOS不通),这就是所谓的稳态状态,两个晶体管一定有一个不会动作,而CMOS半导体由一组MOSFET所连接而成,如下图所示。在IN端子施以0 V或VCC的电压时,便会启动其中一个或其他MOSFET,但VCC与GND之间几乎没有任何电流,因此,CMOS装置可使用在低功率电路。若简单来说就是整体电路未消耗明显功率就可以使用其中一个FET来工作,就做到了要马儿慢慢走路,又可以不用喂牠吃草。

來源:renesas

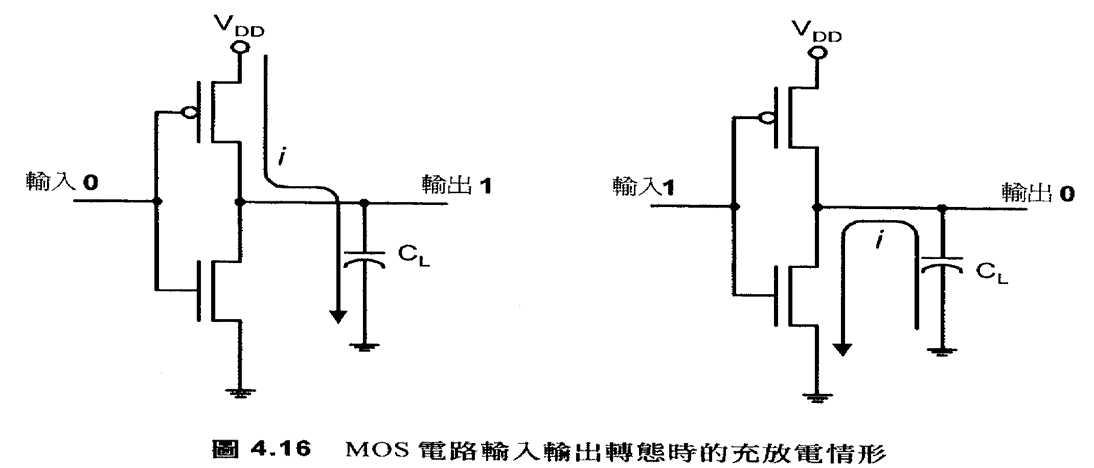

总合来说较大的电子迁移率可以拥有较多整合电路设计的优势,如较高开口率和 RGBW显示及无边框等技术,而这是来自于低功耗技术。詳細的電路結構,请见如下图。在这边你可以观察到PFET有一个圆圈的电路符号在Gate端,此符号为一反相器,其作用为依照Gate电压的指令,对输出端的负载电容C充电至到如Vdd或是放电至0电位;而当Vg(Vin)=Vdd时NFET将会导通而PFET关闭,输出端的部分将会被降至Vout=0V;而当Vg=0,NFET关闭PFET导通,输出端被升压到Vdd,从这个两个稳态状态来看,两个晶体管之中一定会有一个是关闭的模式,故部会有电流从Vdd经由晶体管流到地点(0V的地方),所以CMOS电路的低功耗就是从这来。

来源:Modem Semiconductor Devices of IC

如果是个认真的看倌,你应该看到关键句,稳态状态来看,两个晶体管之中一定会有一个是关闭的模式。那一定就有动态状态,动态状态与静态状态,其功率的变化是当电路有输入输出变化(就是正在工作)才会有功率消耗,同时功率消耗的量是与输入输出变化的量成正比,所以当工作的越快就会消耗越多的功率,是电路功率消耗的主因。

接下来我们要看一下数学的东西:

假设:Pd为动态功率、Psc为短路功率、Ps为切换功率。

Pd=Psc+Ps

Psc为短路功率,其原因为当输出电压约在转态50%电源电压,NMOS及PMOS会同时被导通,进而造成Vdd到地点之间会有通路形成,可以假想上图从Vdd走到PFET的S跟D,然后经过NFET的D和S来到0V,就这样有通道了,因此就有功率的消耗。

Ps=a*f*CL*Vdd^2

a为01或是10之间的机率

CL为负载电容

f为01或是10每秒变化的次数

来源:Introduction to VLSI Circuits and Systems

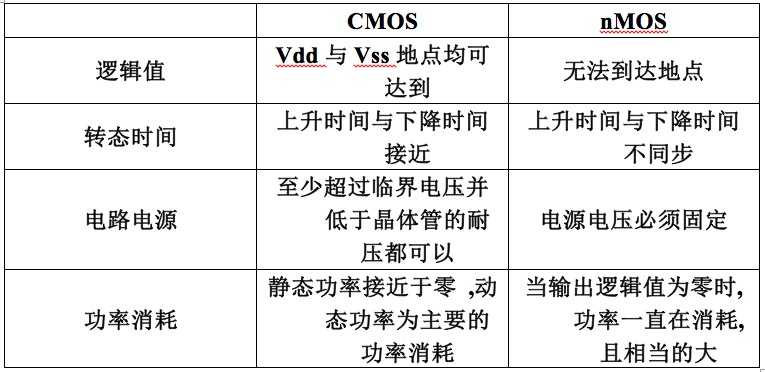

所以简单地归纳一下,如表中所述:

从实务中的例子来看,华星光电曾提出一个利用CMOS作为GOA的设计,主要是通过在各级GOA单元中设置电性连接输出缓冲模块与信号处理模块的反馈调节模块,使得在扫描驱动信号变为高电位时,通过反馈调节模块中N型TFT的正反馈作用使得信号处理模块的下拉能力增强,从而减少扫描驱动信号(G(N))波形的上升时间;在扫描驱动信号作用完毕变为低电位时,通过反馈调节模块中P型TFT的正反馈作用使得信号处理模块的上拉能力增强,从而减少扫描驱动信号波形的下降时间;即能够降低扫描驱动信号的阻容负载,提高驱动高分辨率显示面板时的稳定性。而GOA技术,是利用薄膜晶体管(Thin FilM Transistor,TFT)液晶显示器阵列制程将栅极扫描驱动电路制作在薄膜晶体管阵列基板上,以实现逐行扫描的驱动方式,具有降低生成产本和实现面板窄边框设计的优点,为多种显示器所使用。GOA电路具有两项基本功能:第一是输出扫描驱动信号,驱动面板内的栅极线,打开显示区内的TFT,以对像素进行充电;第二是移位寄存功能,当第N个扫描驱动信号输出完成后,通过时钟控制进行第N+1个扫描驱动信号的输出,并依次传递下去。而这个逐行扫描的驱动方式就是依赖随着LTPS半导体薄膜晶体管的发展整合液晶显示器的面板周边集成电路。

因此很简单的收敛上面的知识,有较大的载子迁移率的材料因为可以达到TFT面积缩小化以及周边可集成电路化采用CMOS,而CMOS又因为具有PFET跟NFET在静态时功率消耗是极低的,因此可充分发挥高载子迁移率材料的优势达到耗电低、厚度薄以及分辨率高等优点。